30 Years of SPARC systems is this month in July’1987 when Sun 4/260 was launched. A month before, I started my professional career at Sun – to be exact June 15, 1987. 16+ years of my professional life was shaped by Sun, SPARC, Systems and more importantly the whole gamut of innovations that Sun did from chips to systems to operating systems to programming languages, covering the entire spectrum of computing architecture. I used to pinch myself for getting paid to work at Sun. It was one great computer company that changed computing landscape.

The SPARC story starts with Bill Joy without whom Sun would not be in existence (Bill was the fourth founder, though) as he basically drove re-inventing computing systems at Sun and thus the world at large. Bill drove technical direction of computing at Sun and initiated many efforts – Unix/Solaris, Programming languages, RISC to name a few. David Patterson (UC Berkeley, now at Google) influenced the RISC direction. [David advised students who changed the computing industry and seems like he is involved with the next shift with TPUs @ Google – more later]. I call out Bill amongst the four (Andy Bechtolsheim, Scott Mcnealy, Vinod Khosla) in this context as without Bill, Sun would not have pulled the talent – he was basically a big black hole that sucked all talent across the country/globe. Without that talent, the innovations and the 30 year history of computing would not have been possible. A good architecture is one that lives for 30 years. This one did. Not sure about the next 30. More on this later. Back then, I dropped my PhD on AI (was getting disillusioned with then version of AI) for a Unix on my desktop and Bill Joy. Decision was that simple.

From historic accounts, the SPARC sytem initiative started in 1984. I joined Sun when the Sun 4/260 (Robert Garner was the lead) was going to be announced in July. It was VME based backplane built both as a pedestal computer (12 VME boards) as well as rack mount system replaced then Sun 3/260 and Sun 3/280. It housed the first SPARC chip (Sunrise) built out from gate arrays with Fujitsu.

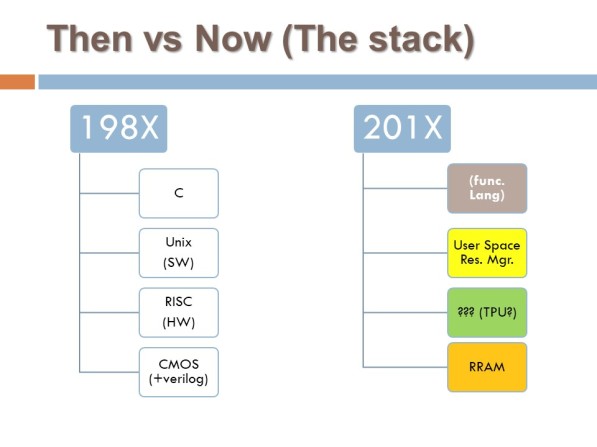

This was an important product in the modern era of computing (198X-201X). 1985-87 was the beginning of exploitation of Instruction level parallelism (ILP) with RISC implementations from Sun and MIPS. IBM/Power followed later, although it was incubated within IBM earlier than both . The guiding principles being, compilers can do better than humans and can generate code that is optimal and simpler with the orthogonal instruction set. The raging debate then was “can compilers beat humans in generating code for all cases”?. It was settled with the dawn of the RISC era. This was the era when C (Fortran, Pascal, ADA were other candidates) became the dominant programming language and compilers were growing leaps and bounds in capabilities. Steve Muchnik led the SPARC compilers, while Fred Chow did with MIPs. Recall the big debates about register windows (Bill even to-date argues about the decision on register windows) and code generation. In brief it was the introduction of pipelining, orthogonal instruction sets and compilers (in some sense compilers were that era’s version of today’s rage in “machine learning” where machines started to outperform human ability to program and generate optimized code).

There were many categories enabled by Sun and the first SPARC system.

- The first chip was implemented in a gate array, which was more cost effective as well as faster TTD (Time to Design). The fabless semiconductor was born out of this gate array model and eventually exploited by many companies. A new category emerged in the semiconductor business.

- EDA industry starting with Synopsys and their design compiler were enabled and driven by Sun. Verilog as a language for hardware was formalized. It was an event driven evaluation model. Today’s reactive program is yesterday’s verilog (not really, but making a point here that HDL forever was event driven programming).

- Create an open eco-system of (effectively free) licensable architecture. It was followed by Opensource for hardware (OpenSPARC) which was a miserable failure.

The first system was followed by the pizza box (SPARCstation 1) using the Sunrise chip. Series of systems innovations were delivered with associated innovations in SPARC.

- 1987 Sun4/260 Sunrise – early RISC (gate array)

- 1989 SPARCstation 1 (Sunray) – Custom RISC

- 1991 Sun LX (Tsunami) – First SoC

- 1992 SPARCstation 10 (Viking) – Desktop MP

- 1992 SPARCserver (Viking) – SMP servers

- 1995 UltraSPARC 1, Sunfire (Spitfire) – 64 bit, VIS, desktop to servers

- 1998 Starfire (Blackbird), Sparcstation 5 (Sabre) – Big SMP

- 2001 Serengeti (UltraSPARC III) – Bigger SMP

- 2002 Ultra 5 (Jalapeno) – Low Cost MP

- 2005 UltraSPARC T-1 (Niagara) – Chip Multi-threading

- 2007 UltraSPARC T-2 – Encryption co-processor

- 2011 SPARC T4

- 2013 SPARC T5, M5

- 2015 SPARC M7 (Tahoe)

- 2017 M8…

The systems innovations were driven by both SPARC and Solaris or SunOS back then. There are 2 key punctuations in the innovation and we have entered the third era in computing. The first two was led by Sun and I was lucky to be part of that innovation and be able to shape that as well.

1984-1987 was the dawn of the ILP era, which continued on for the next 15 years until thread level parallelism became the architectural thesis thanks to Java, internet and throughput computing. A few things that Sun did was very smart. That includes

- Took a quick and fast approach to implement chip by adoption of gate arrays. This surprised IBM and perhaps MIPS w.r.t speed of execution. Just 2 engineers (Anant Agrawal and Masood Namjoo) did the integer unit. No Floating point. MIPS was meanwhile designing a custom chip

- It was immediately followed by Sunrise a full custom chip done with Cypress (for Integer unit) and TI (for floating point unit). Of all the different RISC chips that were designed around the same era, SPARC along with MIPS stood out (eventually Power).

- That was the one two punch enabled by Sun owning the architectural paradigm shift (C/Unix/RISC) as compute stack of then.

Industry’s first Pipelining, super scalar (more than 1 instruction/clock) became the drivers of performance. Sun innovated both at the processor level (with compilers) and system level with symmetric multi-processing with operating system to drive the ‘attack of the killer micros‘. A number of success and failures followed the initial RISC (Sunrise based platform).

- Suntan was an ECL sparc chip that was built, but not taken to market for two reasons. [Have an ECL board up in my attic]. The debate of CMOS vs ECL was ending with CMOS rapidly gaining speed-power ratio of ECL and more importantly the ability of Sun to continue with ECL would have drained the company relative to the value of the high end of the market. MIPS carried through and perhaps drained significant capital focus by doing so.

- SuperSPARC was the first super scalar process that came out in 1991 working with Xerox, Sun delivered the first glue-less SMP (M-bus and X-bus).

- 1995 was a 64 bit CPU (MIPS beat to market – but was too soon) with integrated VIS ( media SIMD instructions)

After that the next big architectural shift was multi-core and threading. It was executed with mainstream Sparc but accelerated with the acquisition of Afara and its Niagara family of CPUs. If there is a ‘hall of fame’ for computer architects, a shout out goes to Les Kohn who led two key innovations – UltraSPARC (64bit, VIS) and UltraSPARC T-1 (multi-threading). Seeds of that shift was sown in 1998 and family of products exploiting multi-core and threading were brought to market starting in 2002/2003.

1998, in my view is the dawn of the second wave of computing in the modern era (1987-2017) in the industry and again Sun drove this transition. The move to web or cloud centric workloads, the emergence of Java as a programming language for enterprise and web applications enabled the shift to TLP – Thread Level Parallelism. In short, this is classical space-time tradeoff where clock rate had diminishing returns and shift to threading and multi-core began with the workload shift. Here again SPARC was the innovator with multi-core and multi-threading. The results of this shift started showing in systems around 2003 – roughly 15 years after the first introduction of SPARC with Sun 4/260. In that 15 years, computing power grew by 300+ times and memory capacity grew by 128 times, roughly following Moore’s law.

While the first 15 years was the ILP era and the 2nd 15 years was about multi-core and threading (TLP). What is the third? We are dawning upon that era. I phrase it as ‘MLP’- memory level parallelism. Maybe not. But we know a few things now. The new computing era is more ‘data path’ oriented – be it GPU, FPGA or TPU – some form of high compute throughput matched by emerging ML/DL applications. A number of key issues have to be addressed.

Every 30 years, technology, business and people have to re-invent themselves otherwise they stand to whither away. There is a pattern there.

There is a pattern here with SPARC as well. SPARC and SPARC based systems have reached 30 year life and it looks to be at the beginning of the end , while a new generation of processing is emerging.

Where do go from here? Defintely applications and technologies are the drivers. ML/DL is the obvious driver. Technologies range from memory, coherent ‘programable datapath accelerators’, programming models (event driven?), user space resource managers/schedulers and lots more. A few but key meta trends

- The past 30 years – Hardware (Silicon and Systems) aggregated (for e.g. SMP) the resources while Software disaggregated (VMware). I believe the reverse will be true for the next 30 i.e. disaggregated hardware (e.g. accelerators or memory) but software will aggregate (for e.g. vertical NUMA, heterogenous schedulers).

- Separation of control flow dominated code vs data path oriented code will happen (early signs with TPUs).

- Event driven (for e.g. reactive) programming models will become more prevalent. The ‘serverless’ trend will only accelerate this model as traditional programmers (procedural) have to be retrained to do event driven programming/coding (Hardware folks have been doing for decades).

- We will build machines that will be hard (not in the sense of complexity – more in the sense of scale) for humans to program.

CMOS, RISC, Unix and C was the mantra in 1980s. Its going to be memory (some form of resistive memory structure) and re–thinking of the stack needs to happen. Unix is also 30+ years old.

Just when you thought Moore’s law is slowing, the amalgamation of these emerging concepts and ideas in a simple but clever system will rise to the next 30 years of innovations in computing.

Strap yourself for the ride…

good history of Sun. One correction – HP PA was the first RISC processor that was launched in 1985 on two product lines HP 3000/MPE-XL (Commercial Systems) and HP 9000/HPUX (Technical Systems). Sun’s Sparc RISC came later. PA RISC was a much better architecture – having worked on PA RISC/MPE XL (8 years) and on Ultrasparc/Solaris (12 years).

LikeLike

IBM 801: 1980 (work started in 1975)

PA-RISC: 1986.

MIPS: 1986

SPARC: 1987 (processor was earlier – 1986).

LikeLike

Renu, if my memory serves me correctly, we called the first SPARC chip Sunrise and the second one Sunray. You have those reversed. No big deal as the blog is very interesting indeed.

Arun Taneja

LikeLike

That’s right. Fixed

LikeLike

fixed it. I had it right later in the writeup. Thanks for catching.

LikeLike